This is the second 8.5 digits DMM in my lab and I'm very excited to own it!

This post includes the following topics:

- Modifications : the new temperature set point for the voltage reference for increasing long term stability and the fan noise reduction.

- Maintenance : Replacing batteries for calibration SRAM and the fan filter.

- Testing some DMM's parameters : noise, leakage current, 1 day and 90 days stability, CAL? 72, and INL against programmable Josephson voltage standard.

- Some useful subroutines loaded with the AR-488 GPIB adapter.

Modifications

The default temperature set point for LTZ1000A Voltage reference was reduced with soldering 100K resistor in parallel to the 15K resistor. This modification improve the long-term stability of the voltage reference. I followed the instructions from Dr. Frank and Illya Tsemenko from xDevs.com. The used resistor model is RNC90Z from Alpha Electronics/VishayPG with max 2ppm/°C TCR.

WARNING : This modification will require a fresh new adjustments of your DMM and will need time the new zener voltage to be stabilized.

The resistor was placed in the X411 component designator. The soldered vias were un-soldered with the help of needle and solder iron.

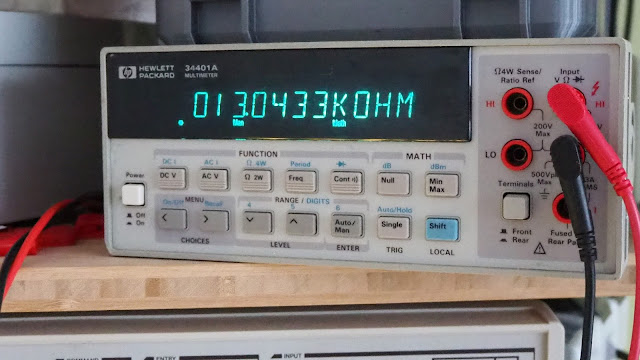

The measured equivalent resistance was near to 13K which match with the LTZ1000(A) datasheet value.

The next modification I made was the fan noise reduction. When the DMM is stored in a rack located in industrial/metrology laboratory, this is not a big problem, but at home the fan noise is very annoying.

The selected fan for replacement was Noctua NF-A6x25 FLX with 2 adapters for reducing the fan speed to 2400 and 1600 rpm. Those adapters are actually just resistors to lower the input voltage. Because the fan voltage of the 3458a is 15V, these adapters are very handy to ensure that the fan voltage does not exceed the 13.2V limit of the Noctua fan.

In result, the noise was reduced significantly and actually is much silent from my second 8.5 digits DMM - Advantest R6581T. There is still noise, but in very acceptable levels.

After replacing the fan, the internal temperature increased with 4°C : the differences between the ambient and internal temperature was 12°C with the old and 16°C with the new fan.

Maintenance

The batteries which keeps the calibration constants in the RAM were replaced. Very comprehensive information about the replacement process can be found in the Martin Lorton's video.

The closest to the original fan filter which I was able to found was the 30 PPI polyurethane foam filter made by company named Multicomp Pro. The part number is MC32657 and can be purchased from Farnell.

You can see in the picture the original filter in the left and the replacement in the right:

Testing some DMM parameters

Noise

The noise measurements were performed with a short PCB across input binding posts and enabled the "Auto Zero" option. The "Digits" column calculates effective number of digits based on standard deviation results for 68% probability. The "RMS noise limit, uV" column data are calculated according the "Additional Errors" and "*RMS noise " tables in the 3458a datasheet.

The time for measurement was 200 seconds for every range and NPLC.

The 0.1/1/10V ranges for 1 and 100 NPLC were in the spec, but out of the spec for 10 NPLC with around 0.02 ppm.

| Range, V | NPLC | Samples | STDEV/RMS noise, uV | RMS noise limit, uV | Digits |

| 10 | 100 | 50 | 0.081 | 0.1 | 8.17 |

| 1 | 100 | 50 | 0.021 | 0.02 | 7.76 |

| 0.1 | 100 | 50 | 0.019 | 0.02 | 6.80 |

|

| 10 | 10 | 500 | 0.269 | 0.25 | 7.65 |

| 1 | 10 | 500 | 0.066 | 0.05 | 7.26 |

| 0.1 | 10 | 500 | 0.074 | 0.05 | 6.21 |

|

| 10 | 1 | 5000 | 0.541 | 1 | 7.35 |

| 1 | 1 | 5000 | 0.137 | 0.2 | 6.94 |

| 0.1 | 1 | 5000 | 0.111 | 0.2 | 6.03 |

Leakage current

The leakage test was performed with 1 and 10 MOhms resistors attached to the binding posts. The measured generated voltage was converted to the leakage current. All measurements are within the 20pA limit at 25°C.

| R input | Range | Leakage, pA |

|

| 1 MOhms | 10 V | 1.66 |

| 1 MOhms | 1 V | 0.75 |

| 1 MOhms | 0.1 V | 1.7 |

|

| 10 MOhms | 10 V | 0.74 |

| 10 MOhms | 1 V | 2.33 |

| 10 MOhms | 0.1 V | 1.7 |

One day stability

In period of 10 days, I measured the LTZ1000 zener output voltage after performing ACAL. I choose the zener output (7.15V) instead the 10V because it should be more thermal stable. The difference between current day and previous day was recorded and shown in the following chart. The 24 hour spec limit for accuracy in the 10V range is 0.5ppm from the reading and 0.05ppm from the range. For the 7.15V zener output this is ~0.4ppm. For two consecutive days, this limit was exceeded with less than 0.15ppm. The recorded ambient and DMM internal temperature peak to peak value was ~2.67°C and standard deviation was ~0.8°C.

90 days stability

In period of 93 days with 3 week interruption, the 10V output from the voltage reference was recorded and the stability was better than +/- 1ppm which is in the spec limit of the 3458A 90 days relative accuracy: 4.15ppm for 10V. During this period, the recorded ambient and DMM internal temperature peak to peak value was ~5.55°C and standard deviation was ~1.21°C.

CAL? 72 calibration constant test

According service note SN18A from Keysight, the DMM can have short term drift more than 0.43ppm daily. To verify this issue, at least 7 days data should be recorded. I decided to record this constant during the 90 days stability test and here are results. The short-term drift value calculated by the formula given in the service note SN18A was less than 0.02ppm peak to peak, standard deviation 0.005ppm. At the end of the period, the last value of the C variable was 0.005ppm. Far less than the stated 0.43ppm value. I recorded also the day to day drift and the peak to peak value was 0.687ppm, standard deviation 0.162.

Integral nonlinearity measurement against programmable Josephson voltage standard

This is may be the most important parameter when you use a DMM in the metrological field. When you make ratio transfer measurements from one calibrated standard to other one, you want to have the minimum INL. This will minimize your uncertainty budget.

The INL test was performed in the Bulgarian Metrology Institute using their new Josephson programmable voltage standard manufactured by Supracon.

Based on data from the protocol, I made charts against the linearity specification found in the 3458a datasheet. The linearity is within the specified limits, except the 0.1V range.

Using 3458a with GPIB controller

Unfortunately, the 3458a DMM is not very user friendly when it is used from the front panel. It is far away from the Advantest R6581T user interface which can be used almost without reading the documentation available in Japan language only :-) . The only way to get desire functionality during measurements is to write BASIC subroutines. To load them, you need a GPIB controller.

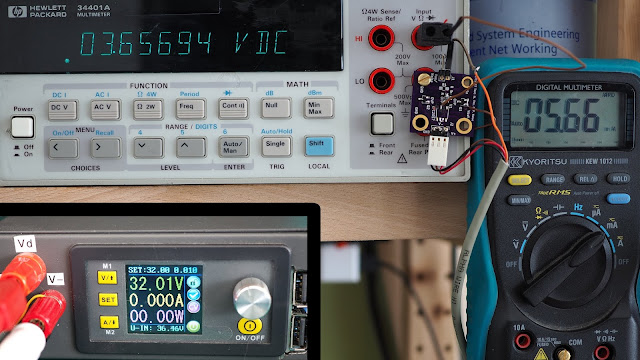

Last year I made

AR488 based GPIB controller which was used to communicate with Advantest R6581T and HP 34401A multimeters. It is enough reliable if you set the BOD voltage to 4.3 for the atmega32u4 microcontroller. The default one is set to 2.6V which cause very often firmware corruption due voltage glitches.

Using Serial/UART port terminal program (like CuteCom under GNU/Linux OS) you have to write only the following commands to enter into the remote mode:

++ren 1

++addr GPIB_ADDRESS

++auto 1

ID?

Where GPIB_ADDRESS is DMM GPIB address set with ADDRESS XX command from the front pannel.

When you upload the subroutines from a file, set value 100ms in the "Char delay" field to avoid errors during transmission.

I made two basic subroutines one of the which makes the real measurements and the second one (STAT_INFO) which display on the DMM's display, the statistical results after the measurements. The result contains number of samples, standard deviation, peak to peak, average, minimum and maximum values. Once the subroutines are loaded into the DMM, they can be invoked with the "CALL SUB_NAME" command. It is very convenient to store "CALL" command in one of the DefKey for fast access to all of your subroutines.

SUB STAT_INFO

REAL MINV, MAXV, MEANV, STDEVV, P2PV, NUMV

RMATHV LOWER, MINV

RMATHV UPPER, MAXV

RMATHV MEAN, MEANV

RMATHV SDEV, STDEVV

RMATHV NSAMP, NUMV

LET P2PV = MAXV-MINV

DSP "N=" NUMV " STDEV=" STDEVV " P2P=" P2PV " AV=" MEANV " MIN=" MINV " MAX=" MAXV

SUBEND

SUB DCV_XXXXXX

PRESET NORM

MEM FIFO

TRIG HOLD

MFORMAT DINT // Store the result in 4 bytes

DCV 10 // Change here the DCV range

NRDGS 15 // Change here the number of samples

NDIG 8

NPLC 100

AZERO ON

DISP MSG

TRIG SGL

MMATH STAT

BEEP

WAIT 500

BEEP

WAIT 500

BEEP

WAIT 500

BEEP

WAIT 500

BEEP

TRIG AUTO

DISP ON

SUBEND