Between the 11 April and 14 May 2020 I tried to measure the 1 month stability of the LTC6655. During this period I made 80 measurements and the result is shown in the following chart:

Project for building an open source, DIY, low-cost and high accuracy digital multimeter.

Sunday, December 27, 2020

Temperature coefficient and the humidity effect on the LTC6655 voltage output

Friday, December 25, 2020

Revised analog front-end : Replacing the analog switch, part 4/4

In the post for the automatic voltage range, I used the analog switch ADG5419 to switch between the low and the high voltage ranges. I was wondering if the switch can be replaced with the shutdown feature of the LTC2057 op-amp. According the datasheet when the LTC2057 is in the shutdown mode : "... the output presents a high impedance to external circuitry". If the outputs of the op-amps are shorted and the SD inputs are feed with opposite signals for each op-amp, in theory this is equivalent to a SPDT switch. The switch is not expensive one (it cost around 5USD), but the maximum voltage which can stand (+/- 22V) was less than the voltage which I will use for the LTC2057HV. So usage of the ADG5419 cost me 2 more power rails which I want to avoid.

Тhis raised the following question : what kind of glue logic ("A" in the schematics above) I have to put between the outputs of the MAX990 comparators and the SD/SDCOM op-amp inputs?

The output pin of the MAX990 is an open drain and a pull-up resistor to the positive rail have to be added. The voltage outputs of the MAX990 are between -2.5V+Vds(of the open-drain stage) when input voltage is above 2.048V and +2.5V when input voltage is below 2.048V.

From the LTC2057 datasheet we have the following information: "Shutdown control is accomplished through differential signaling. This method allows for low voltage digital control logic to operate independently of the amplifier’s high voltage supply rails.". And the tables with the logic and operating voltage ranges:

I thought : why not to put an NOR gate 74x logic? The negative input voltage is not a problem if the Vss is connected to the -2.5V power rail and the Vcc is connected to the +2.5V. So, I made a breadboard proof of concept and putting the scope probe on the shorted outputs of the LTC2057 op-amps, I got a very clean, 2 us transition time between the two input signals.

Sunday, April 26, 2020

Revised analog front-end : Over Voltage Protection, part 3/4

How over-voltage protection works

There is one problem: when a standard LDO is used for positive rail, it can not sink a current. As a result, the current through the diode will increase the voltage on the positive rail and can damage the circuit under the protection.

There are two solutions to this problem: to use a buffer op-amp which can sink between several to tens mA or to use schematics I found during the op-amp selection from the ADA4177 datasheet - an PNP transistor which "re-routes" the current from the diode to the "sinking" ground. I tried the solution in the ADA4177 and it works perfectly.

If a dual-polarity power supply is used for the op-amp, the negative power rail will source the current through the diode and the voltage will not be increased when the input voltage exceeds the negative power rail.

- For the positive over-voltage: the sum of the positive power rail voltage, the diode's forward voltage and the base-emitter voltage of the PNP transistor.

- For the negative over-voltage: the sum of the positive power rail voltage and the forward voltage of the diode.

The clamping voltage must not exceed the maximum allowed power supply of the op-amp. Let's give one example with LTC2057HV that has spec of 60V supply peak to peak voltage (65V absolute maximum). If the op-amp is supplied with +/- 27V, this will give 60V-(2*27V)=6V maximum clamp above the positive or negative power rail. That means that maximum allowed value is +/-33V.

Component Selection

| BAV199/BAS416 | MMBF4117 | BAV199/BAS416 | MMBF4117 | |

| V supply, V | 27 | 27 | 27 | 27 |

| Max reverse voltage, V | 75 | 40 | 75 | 40 |

| Max protection, V | 102 | 67 | 102 | 67 |

| Max current, mA | 160/200 | 50 | 160/200 | 50 |

| Limit resistor, Ohms | 2000 | 2000 | 10000 | 10000 |

| Limit current, mA | 23.5 | 6.0 | 4.7 | 1.2 |

| Limit Resistor Power, W | 1.105 | 0.072 | 0.221 | 0.014 |

| Noise, RMS uV 1pA/√Hz | 0.01 | 0.01 | 0.03 | 0.03 |

| Leakage voltage (100pA), uV | 0.20 | 0.20 | 1.00 | 1.00 |

The test

|

| Additional circuits for the current sink. |

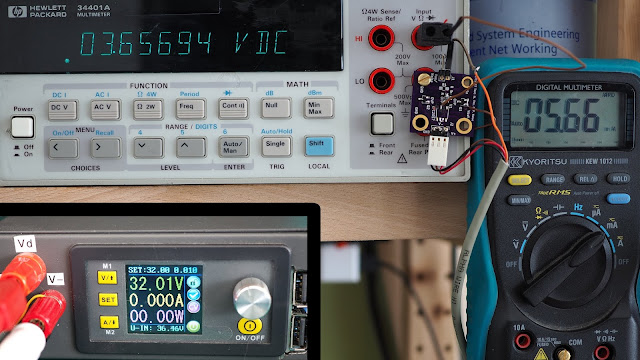

- The input voltage was set from 0 to 32V with 1V step using the DPS 3003

|

| Test without the current sink circuit. |

|

| Test with the current sink circuit. |

- The input voltage was set from 2 to -30V with 1V step using the negative LDO.

Sunday, March 29, 2020

Revised analog front-end : op-amp selection and test, part 2/4

Selection of op-amps

In the previous post I made error budget for op-amp parameters and now I have to select available op-amps on the market. I made 3 groups of them :

- op-amps capable to handle input signals up to +/- 22V full scale range.

- op-amps capable to handle input signals up to +/- 12V full scale range.

- op-amps with errors below my threshold, but with maximum power supply under 10V. Using bootstrap schematics they can be used for input signals up to 22V. It's kind of a back-up plan if the previous 2 group failed.

Additionally I added the OP-27GS and LTC1050C as comparison to the selected op-amps.

The error budget is:

- Ibias less then 50pA

- Voltage noise, p2p value less than 4.4uV for the 22V range and less than 2.4uV for the 12V range. This is equivalent to 7 digits. The test for this parameter will be performed with short between positive input and the ground.

- Current noise density, RMS value less than 1041 fA/√Hz for 22V Range and 557 fA/√Hz for 12V Range. My criteria for this threshold is to reach a 6 digits when the input resistance is 1MOmhs and take into account the previous voltage noise thresholds.

- Estimated Effective Number Of Digits (ENOD) for 99.7% probability. Combining voltage noise, current noise density and the input resistance must provide at least 6 digits for 12V or 22V ranges when input resistance is 1MOhms or at least 7 digits when the inputs are short. The used formula is:

- Input Voltage offset (by temperature, by time and initial value) : less than 1uV/°C and less than 1uV per month none cumulative. The initial value is not so important because it will be calibrated anyway.

- Input resistance of the op-amp : at least 100GOhm

- CMRR : minimum 120dB

| Voltage Range, V | 22 | 12 | 12 | 12 | |||||

| Manufacturer | LT/AD | AD | Microchip | TI | TI | LT/AD | Agilent 34401 | Keithley 2000 | |

| Prio | Parameter ↓ / Op-amp -> | LTC2057HV | ADA4522 | MCP6V51 | OPA140 | OPA192 | LT1024A | OP-27GS | LTC1050C |

| 1 | IBias, typ pA | 30 | 50 | 60 | 0.5 | 5 | 25 | 15000 | 20 |

| IBias, max pA | 200 | 150 | 250 | 10 | 20 | 120 | 80000 | 125 | |

| 2 | Voltage Noise p2p, typ uV | 0.22 | 0.117 | 0.21 | 0.25 | 1.3 | 0.5 | 0.09 | 1.6 |

| 2 | Current Noise RMS fA/√Hz | 130 | 1100 | 4 | 0.8 | 1.5 | 20 | 600 | 1.8 |

| Est. p2p noise Rin=1MOhm, uV | 3.84 | 23.10 | 2.72 | 2.72 | 3.00 | 2.78 | |||

| 2 | Est. ENOD Rin=1MOHms | 7.06 | 6.28 | 7.21 | 6.95 | 6.90 | 6.94 | ||

| 2 | Est. ENOD Rin=0Ohms | 8.30 | 8.58 | 8.32 | 8.25 | 7.53 | 7.94 | ||

| 3 | Vos Tdrift, typ uV/C | N.A. | 0.006 | 0.005 | 0.35 | 0.1 | 0.25 | 0.4 | 0.01 |

| 3 | Vos Tdrift, max uV/C | 0.025 | 0.03 | 0.031 | 1 | 0.5 | 1.5 | 1.8 | 0.05 |

| 3 | Vos long-term month uV | near zero | near zero | 2 | N.A. | N.A. | 0.3 | 2 | 0.05 |

| Vos, typ uV | 0.5 | 1.5 | 2.4 | 30 | -/+ 5 | 15 | 55 | 0.5 | |

| Vos, max uV | 5 | 7 | 15 | 120 | -/+ 25 | 50 | 200 | 5 | |

| 4 | Rin, GOhms | N/A | 1000 | 120 | 10000 | 10000 | 2000 | 2 | N/A |

| 5 | CMRR, min dB | 133 | 140 | 135 | 126 | 120 | 112 | 100 | 114 |

| Vsupply max V | -/+30 | -/+27.5 | -/+24.75 | -/+18 | -/+18 | -/+20 | -/+22 | -/+9 | |

| Price, USD w/o tax, Mouser | 5.29 | 2.68 | 1.32 | 3.61 | 2.68 | 16.07 | 3.56 | 5.78 | |

- In the LTC2057 datasheet, the input noise current spectral density for +/- 30V is specified as 130 fA/√Hz, but later it's stated that "The DC average of injection current is the specified input bias current, but this current has a frequency component at the chopping frequency as well. When these small current pulses, typically about 0.7nA RMS, interact with source impedances or gain setting resistors, the resulting voltage spikes are amplified by the closed loop gain". I never got the value of 130 fA/√Hz with 1MOhms input resistance, but the measurements were close to the mentioned 0.7nA.

- In the ADA4522 datasheet, the current noise density for 55V is specified as 800 fA/√Hz, but for a gain of 100. Later in Figure 78 for a gain of 1, voltage supply of +/- 27.5V and input resistance of 100KOhms, the current noise density is about 1100 fA/√Hz for 10Hz-1KHz bandwidth.

| Voltage Range with bootstrap, V | 22 | |||||

| Manufacturer | AD | TI | LT/AD | TI | TI | |

| Prio | Parameter ↓ / Op-amp -> | ADA4530 | ICL7652 | LTC1052C | TLC2654AC | OPA376 |

| 1 | IBias, typ pA | 0.001 | 4 | 1 | 50 | 0.2 |

| IBias, max pA | 0.02 | 30 | 30 | 60 | 10 | |

| 2 | Voltage Noise p2p, typ uV | 4 | 2.8 | 1.5 | 1.5 | 0.8 |

| 2 | Current Noise RMS fA/√Hz | 0.07 | 4 | 0.6 | 4 | 2 |

| Est. p2p noise Rin=1MOhm, uV | 4.83 | 3.89 | 3.09 | 3.10 | 2.82 | |

| 2 | Est. ENOD Rin=1 MOHms | 6.70 | 6.79 | 6.89 | 6.89 | 6.93 |

| 2 | Est. ENOD Rin=0 Ohms | 7.04 | 7.20 | 7.47 | 7.47 | 7.74 |

| 3 | Vos Tdrift, typ uV/C | 0.13 | 0.003 | 0.01 | 0.01 | 0.26 |

| 3 | Vos Tdrift, max uV/C | 0.5 | 0.05 | 0.05 | 0.05 | 1 |

| 3 | Vos long-term month uV | ~1.5 | 0.06 | 0.1 | 0.02 | N.A. |

| Vos, typ uV | 9 | 0.6 | 0.5 | 4 | 5 | |

| Vos, max uV | 50 | 5 | 5 | 10 | 25 | |

| 4 | Rin, GOhms | > 100000 | N/A | N/A | N/A | N/A |

| 5 | CMRR, min dB | 110 | 110 | 120 | 110 | 76 |

| Vsupply max V | -/+8 | -/+8 | -/+8 | -/+8 | -/+2.5 | |

| Price, USD wo tax | 23.47 | 6.09 | 8.77 | 5.92 | 1.69 | |

Description of the tests

Using the 8.5 digits Advanttest R6581T DMM I will do the following tests for the selected op-amps :- Ibias with 1MOhm resistor connected between the positive input and the ground.

- RMS and peak to peak noise with 1MOhms input resistance.

- RMS and peak to peak noise with short inputs.

- Vos with short inputs.

- Measuring voltage difference between input and output voltage vs. variations in the input voltage. I call this kind as linearity. In ideal case the differences between the input and output voltage of unity gain op-amp must not depend on changes of the input voltage and this difference must be constant. The measurement value is equal to (Max(∆(Vout-Vin)) / ∆Vin) * 1E+6 (ppm).

- the bypass capacitors, so I have to solder them at the back of the PCB near to the supply pins. Without them the results are really scrappy.

- to add guard ring around the input positive terminal of the op-amp. This is a recommendation found in the datasheets for current leakage limitation.

- the possibility to disconnect the 1MOhms resistor from the ground that is required for the linearity test.

- the load resistor between the op-amp output and the ground.

Other tests which can be made, but I do not have proper equipment or the time for that:

- Vos long term drift.

Results from the tests

| R6581 | HP 34401 | Keitley 2000 | Keitley 2002 | |||||

| STDEV, uV | P2P, uV | STDEV, uV | P2P, uV | STDEV, uV | P2P, uV | STDEV, uV | P2P, uV | |

| Vnoise Zero | 0.06-0.106 | 0.2-0.3 | 0.48-0.6 | 2-2.5 | 0.834-0.88 | 3.44-4 | 0.598-0.734 | 2.92-3.37 |

| ENOD Zero | 8.3-8.05 | 8.08-7.9 | 7.4-7.3 | 7.08-6.98 | 7.16-7.13 | 6.8-6.77 | 7.56-7.47 | 7.17-7.11 |

| Vnoise 1M | 0.197-0.347 | 1-2.7 | 0.514-0.714 | 2.1-3.5 | 2.38-3.64 | 10-20 | 1.58-1.95 | 26.13-28.95 |

| ENOD 1M | 7.78-7.53 | 7.38-6.95 | 7.36-7.23 | 7.06-6.83 | 6.7-6.5 | 6.38-6.07 | 7.14-7.05 | 6.22-6.18 |

Results with

test board ver. 1 |

Package

|

Vos, uV

|

Ib, pA

min- max |

Ib, pA

max spec |

Linearity,

ppm Rout = open |

Linearity,

ppm Rout=10K | Noise, uV | |||

| Zero, STDEV | Zero, p2p | 1M, STDEV | 1M, p2p | |||||||

| LTC2057HV 1 | soic-8 | 3 - 6 | 53.66 - 62.19 | 200 | 0.491 | 1.291 | 0.107 - 0.159 | 0.4 - 0.7 | 1.257 - 1.97 | 5.73 - 9 |

| LTC2057HV 2 | soic-8 | 0.9 - 7.2 | 688 - 736 | 200 | 0.473 | 1.214 | 0.113 - 0.201 | 0.4 - 0.9 | 1.767 - 7.65 | 6.4 - 34.4 |

| LTC2057HV 3 | msop-8 | 5.4 - 7 | 12.9 - 33.5 | 200 | N.A. | N.A. | 0.117 - 0.230 | 0.5 - 1.1 | 1.59 - 2.62 | 7.2 - 11.8 |

| ADA4522 1 | soic-8 | -0.2 - 0.3 | 1002.4 - 1004.7 | 150 | 0.055 | 0.059 | 0.128 - 0.118 | 0.4 - 0.6 | 1.63 - 5.44 | 6.7 - 30 |

| ADA4522 2 | soic-8 | 0.8 - 1.8 | 692 - 695 | 150 | 0.1 | 0.036 | 0.112 - 0.243 | 0.6 - 0.8 | 3.26 - 10.7 | 15.8 - 43.8 |

| MCP6V51I 1 | msop-8 | -0.2 - -0.3 | 5502 - 5510 | 250 | N.A. | |||||

The only op-amp which passed the bias current tests was the third sample in msop-8 package. The first one was very close to the 50 pA limit. The second sample was 3-4 times above the specification limit. The rest of the op-amps failed as well.